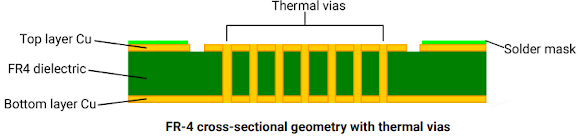

Enhancing thermal transfer for FR-4 PCBs can be achieved cost-effectively by incorporating thermal vias and plated through-holes (PTH) between conductive layers. These methods efficiently dissipate heat and improve the overall performance of the PCB.

Key design considerations for vias include:

- Adhering to the manufacturer's recommended number of holes (thermal vias) in the thermal pad area to ensure optimal thermal transfer.

- Connecting all holes within and outside the thermal pad area to the internal ground plane or other internal copper plane, thus maximizing the thermal dissipation efficiency.

- Employing a direct or solid connection to achieve lower thermal resistance for the internal ground plane, contributing to improved overall thermal performance.

Furthermore, for the bottom copper plane, it is recommended to encircle the vias with a ring of exposed copper (0.05 mm wide) to prevent excessive voiding. This practice, as detailed in the TI Application Report SLOA120–May 2006, ensures optimal thermal transfer and reliability.